Categories

Statistics

Since 08.08.2014

Counts only, if "DNT = disabled".

Your IP is 18.191.189.119

ec2-18-191-189-119.us-east-2

Counts only, if "DNT = disabled".

Your IP is 18.191.189.119

ec2-18-191-189-119.us-east-2

Info

เราจะทำแบบวิศวกรผู้ยิ่งใหญ่

25. December 2024

YOU RATED THIS ...

avg = 0.0 , n = 0

MERRY CHRISTMAS

CETH-60-Counter.php 12794 Bytes 12-02-2018 11:22:30

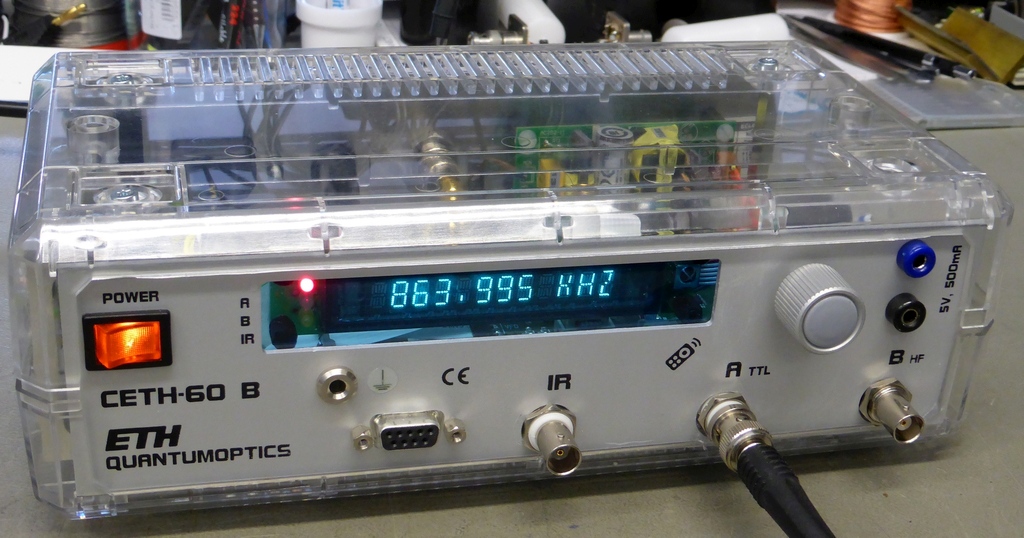

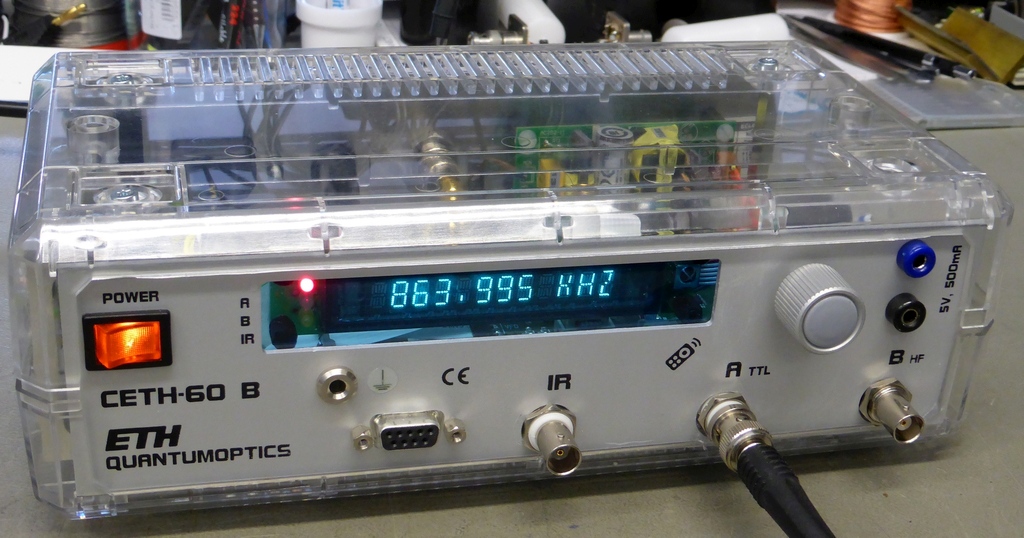

ELECTRONIC PROJECTS : CETH-60

60 MHz Frequency Counter, expandeable to ~ 17 GHz.

Yet another counter. Yes, but this bargain VFD insisted on "buy me".

Secondly we needed a display for all of those prescalers, and last but not least we would like to propose a circuit based on the SN74LV8154PW which

is not that popular - probably due to the very small case ?

Circuit Description

The Design is straightforward. Two channels, of which one is a TTL compatible input allow displaying of frequency ratios or differences.

Both inputs are protected against overvoltage. The third one is an output, as the VFD contains an IR receiver. A lot of possible reference

sources are possible : standard cmos crystal oscillator, ocxo or external standard.

The GATE signal is derived from the 10 MHz source of your choice. It is heavily divided by 2 to finally get a symmetrical gate clock of 2.384 Hz or 209.71 ms (gate open) per channel. This is important, as one of the 2 channels is always counting, whilst the other one is processed. This allows for a very high speed measurement, when using one channel.

If the input frequency is low, the microprocessor decides if the chain is reset or not. The two inputs and the two counting chains may be routed idividually with a cross switch. This means, that one chain could be reset periodically whils the other one keeps on counting. Filling up 32 bit takes a time :-)

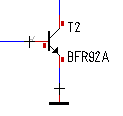

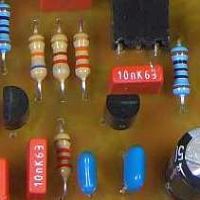

In order to achieve "some" frequency, a prescaler of 2/4 is built in. This should allow for 99999.99 kHz (99'999.9 kHz or 99.999'9 MHz) input frequencies (Display has 12 digits :-).

If a serial module ( RS232, USB or XPORT) is present, the readings will be send by the UART.

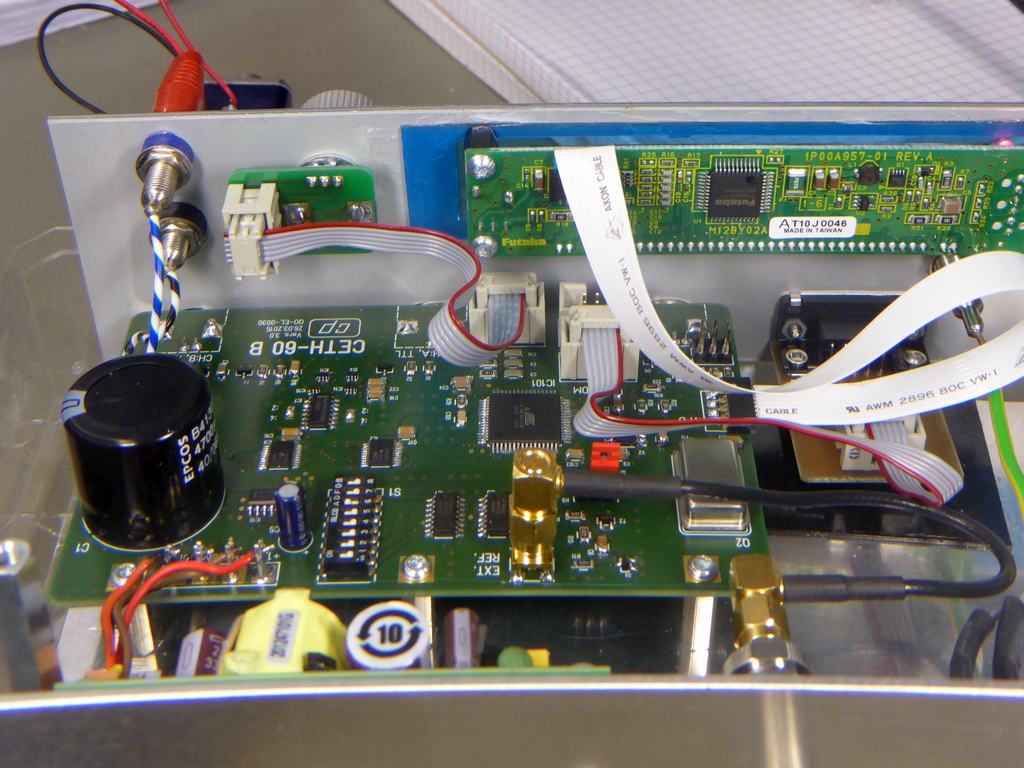

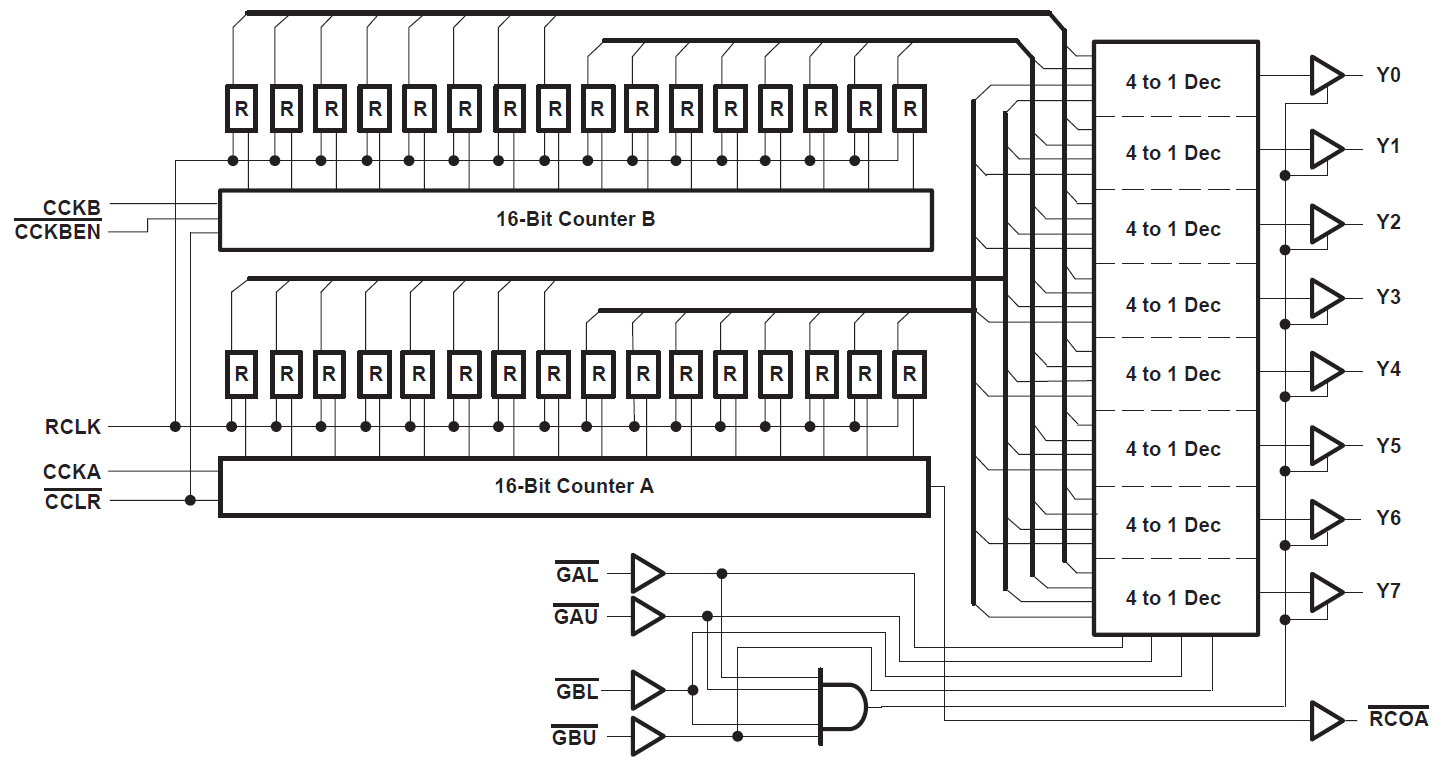

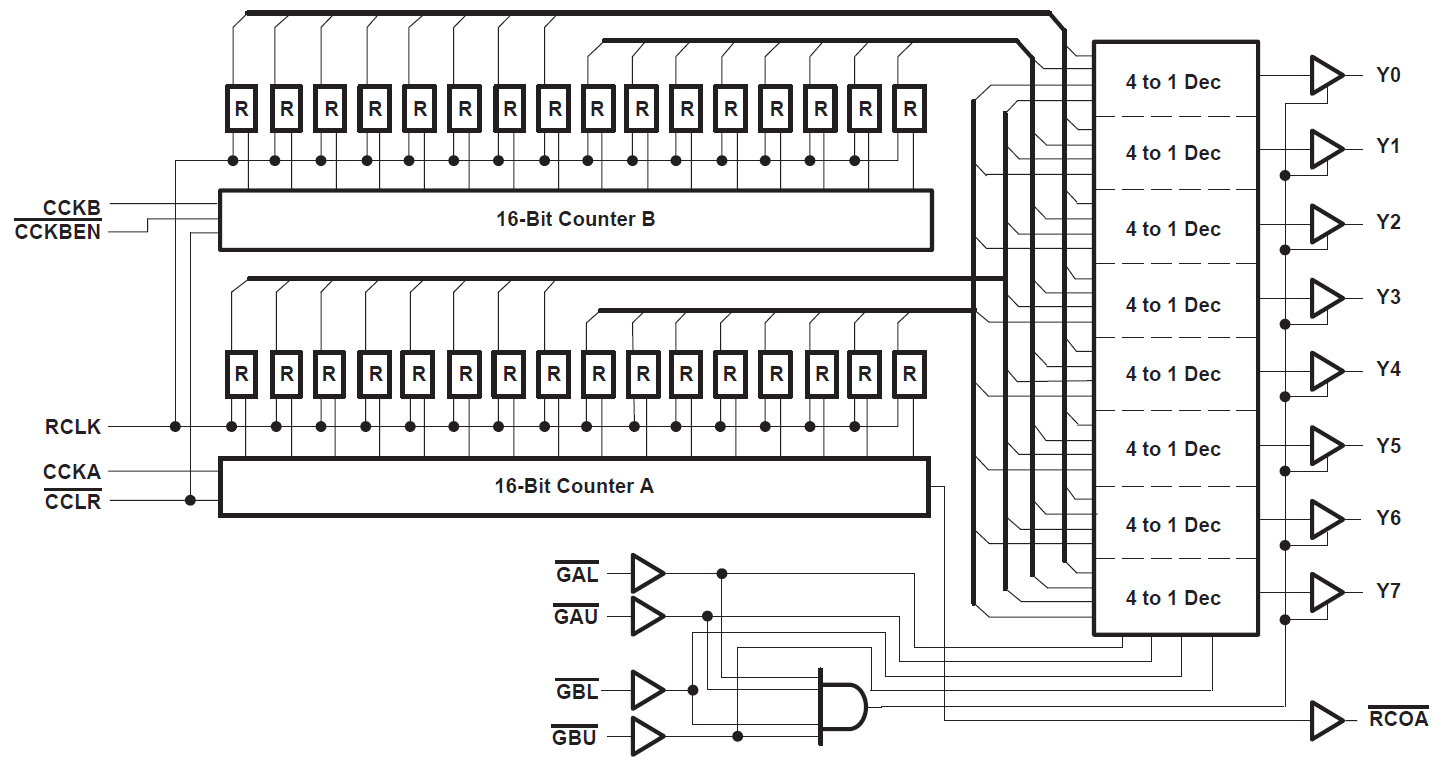

The workhorse of this circuit is the SN74LV8154PW (and his twin), configured as a 32-bit synchronous counter. To achieve that, the clock is connected to CLKA and CLKB. The RCOA is used to enable counter B. The 32 bit can be read as 4 times a 8 bit value. The drawing below shows the block diagram of this circuit. Available at (e.g.) Farnell, CHF 0.82 (2/2015) - if you buy ten pcs.

Block Diagram of the 74LV8154. Drawing courtesy of Texas Instruments.

The GATE signal is derived from the 10 MHz source of your choice. It is heavily divided by 2 to finally get a symmetrical gate clock of 2.384 Hz or 209.71 ms (gate open) per channel. This is important, as one of the 2 channels is always counting, whilst the other one is processed. This allows for a very high speed measurement, when using one channel.

If the input frequency is low, the microprocessor decides if the chain is reset or not. The two inputs and the two counting chains may be routed idividually with a cross switch. This means, that one chain could be reset periodically whils the other one keeps on counting. Filling up 32 bit takes a time :-)

In order to achieve "some" frequency, a prescaler of 2/4 is built in. This should allow for 99999.99 kHz (99'999.9 kHz or 99.999'9 MHz) input frequencies (Display has 12 digits :-).

If a serial module ( RS232, USB or XPORT) is present, the readings will be send by the UART.

The workhorse of this circuit is the SN74LV8154PW (and his twin), configured as a 32-bit synchronous counter. To achieve that, the clock is connected to CLKA and CLKB. The RCOA is used to enable counter B. The 32 bit can be read as 4 times a 8 bit value. The drawing below shows the block diagram of this circuit. Available at (e.g.) Farnell, CHF 0.82 (2/2015) - if you buy ten pcs.

Block Diagram of the 74LV8154. Drawing courtesy of Texas Instruments.

Timing

All the timing is derived from the 10 MHz clock. The 10 MHz is used directly to drive the Atmega128.

The divided clock of 2.384 Hz has a duty cycle of 50 % and is used

to switch the gates. If the gates signal is high, the chain B is counting whilst the chain A is beeing processed. In case of a low,

chain A is counting and chain B is beeing processed. Due to that architecture, one chain is always counting and the microprocessor still has a lot

of time to process the data. This processing can be a simple display of the counts in the registers as well as arithmetics like FREQ B / FREQ A,

FREQ B - FREQ A (for e.g. subtracting an lo offset). A lot of possibilities are imagineable. The firmware offers some basic arithmetics which

the webmaster thought it mayst be of interest, but this can be changed easily !

Menue

The menue structure is like a ring, where a token (or pointer) indicates the current function. Pressing the knob will move horizontally,

whilst rotating the knob moves vertically. The design is open for new functions, which can be easily integrated. The whole 'main' consists

just out of a select / case structure. Three interrupts handle the Rotary Encoder.

Power Supply

As we use only digital circuitry, a switched power supply may be used. This one (ECL05-30) delivers +5V and +12V. The +5V is switched, whilst

the +12V is always on (used for OCXO, XCO).

Display • Futaba M12BY02AA

This vacuum fluorescent display is a milestone of technology developement. Unfortunately from the last century / millennium. The datasheet aka

"engineering proposal" offers only few information.

This makes it a true challenge to get it run. But you are rewarded - with a beautiful (classic) view and a low price.

Infrared Receiver, 37.9 kHz

The IR Receiver was already on the VFD board. As one of my honourable instructors had an impressive counter with an IR receiver from a television,

which was displaying the code of the transmitted command, we wanted to use the existing hardware for sentimental reasons :-)

It can decode the NEC as well as the RC5 protocol. The bitstream is output at the bnc socket labelled "IR". It is also send by the UART, so you may log television zapping behaviour.

It can decode the NEC as well as the RC5 protocol. The bitstream is output at the bnc socket labelled "IR". It is also send by the UART, so you may log television zapping behaviour.

Downloads

✈ Share your thoughts

The webmaster does not read these comments regularely. Urgent questions should be send via email.

Ads or links to completely uncorrelated things will be removed.

Your Browser says that you allow tracking. Mayst we suggest that you check that DNT thing ?

ช้างเผือก

ช้างเผือก